Jurutera-jurutera lain, pernahkah anda mengalami kegagalan "hantu" seperti ini? Gerbang pusat data yang direka bentuk dengan baik telah diuji dengan baik di makmal, tetapi selepas satu atau dua tahun penggunaan besar-besaran dan operasi lapangan, kumpulan tertentu mula mengalami kehilangan paket yang tidak dapat dijelaskan, gangguan bekalan elektrik, dan juga but semula. Pasukan perisian telah menyiasat kod tersebut dengan teliti, dan pasukan perkakasan telah berulang kali memeriksa, akhirnya menggunakan instrumen ketepatan untuk mengenal pasti puncanya: hingar frekuensi tinggi pada rel kuasa teras.

Penyelesaian Kapasitor Berbilang Lapisan YMIN

- Analisis Teknikal Punca Utama – Mari kita selidiki lebih mendalam tentang "analisis patologi" yang mendasari. Penggunaan kuasa dinamik cip CPU/FPGA dalam gerbang moden berubah-ubah secara dramatik, menghasilkan harmonik arus frekuensi tinggi yang banyak. Ini memerlukan rangkaian penyahgandingan kuasa mereka, terutamanya kapasitor pukal, mempunyai rintangan siri setara (ESR) yang sangat rendah dan keupayaan arus riak yang tinggi. Mekanisme kegagalan: Di bawah tekanan jangka panjang suhu tinggi dan arus riak yang tinggi, antara muka elektrolit-elektrod kapasitor polimer biasa terus merosot, menyebabkan ESR meningkat dengan ketara dari semasa ke semasa. Peningkatan ESR mempunyai dua akibat kritikal: Keberkesanan penapisan yang berkurangan: Menurut Z = ESR + 1/ωC, pada frekuensi tinggi, impedans Z ditentukan terutamanya oleh ESR. Apabila ESR meningkat, keupayaan kapasitor untuk menyekat hingar frekuensi tinggi menjadi lemah dengan ketara. Peningkatan pemanasan sendiri: Arus riak menghasilkan haba merentasi ESR (P = I²_rms * ESR). Kenaikan suhu ini mempercepatkan penuaan, mewujudkan gelung maklum balas positif yang akhirnya membawa kepada kegagalan kapasitor pramatang. Akibatnya: Susunan kapasitor yang gagal tidak dapat memberikan cas yang mencukupi semasa perubahan beban sementara, dan juga tidak dapat menapis hingar frekuensi tinggi yang dihasilkan oleh bekalan kuasa pensuisan. Ini menyebabkan gangguan dan penurunan voltan bekalan cip, yang membawa kepada ralat logik.

- Penyelesaian dan Kelebihan Proses YMIN – Kapasitor keadaan pepejal berbilang lapisan siri MPS YMIN direka bentuk untuk aplikasi yang mencabar ini.

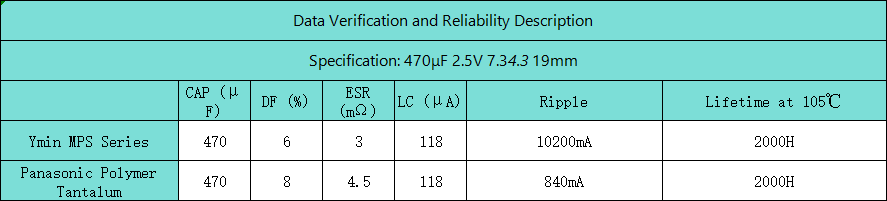

Kejayaan struktur: Proses berbilang lapisan mengintegrasikan berbilang cip kapasitor keadaan pepejal kecil secara selari dalam satu pakej. Struktur ini menghasilkan kesan impedans selari berbanding kapasitor besar tunggal, meminimumkan ESR dan ESL (induktans siri setara) kepada tahap yang sangat rendah. Contohnya, kapasitor MPS 470μF/2.5V mempunyai ESR serendah di bawah 3mΩ.

Jaminan Bahan: Sistem polimer keadaan pepejal. Menggunakan polimer konduktif pepejal, ia menghapuskan risiko kebocoran dan menawarkan ciri frekuensi suhu yang sangat baik. ESRnya berbeza-beza secara minimum dalam julat suhu yang luas (-55°C hingga +105°C), secara asasnya menangani had jangka hayat kapasitor elektrolit cecair/gel.

Prestasi: ESR ultra rendah bermaksud keupayaan pengendalian arus riak yang lebih besar, mengurangkan kenaikan suhu dalaman dan meningkatkan MTBF sistem (masa min antara kegagalan). Respons frekuensi tinggi yang cemerlang menapis hingar pensuisan tahap MHz dengan berkesan, memberikan voltan bersih kepada cip.

Kami menjalankan ujian perbandingan pada papan induk pelanggan yang rosak:

Perbandingan bentuk gelombang: Di bawah beban yang sama, tahap hingar puncak-ke-puncak rel kuasa teras asal mencapai setinggi 240mV. Selepas menggantikan kapasitor YMIN MPS, hingar telah diredam kepada kurang daripada 60mV. Bentuk gelombang osiloskop dengan jelas menunjukkan bahawa bentuk gelombang voltan telah menjadi lancar dan stabil.

Ujian kenaikan suhu: Di bawah arus riak beban penuh (kira-kira 3A), suhu permukaan kapasitor biasa boleh mencapai lebih 95°C, manakala suhu permukaan kapasitor YMIN MPS hanya sekitar 70°C, pengurangan kenaikan suhu lebih 25°C. Ujian hayat dipercepatkan: Pada suhu undian 105°C dan arus riak undian, selepas 2000 jam, kadar pengekalan kapasiti mencapai >95%, jauh melebihi piawaian industri.

- Senario Aplikasi dan Model yang Disyorkan – Siri YMIN MPS 470μF 2.5V (Dimensi: 7.3*4.3*1.9mm). ESR ultra rendah (<3mΩ), penarafan arus riak tinggi dan julat suhu operasi yang luas (105°C) menjadikannya asas yang boleh dipercayai untuk reka bentuk bekalan kuasa teras dalam peralatan komunikasi rangkaian mewah, pelayan, sistem storan dan papan induk kawalan perindustrian.

Kesimpulan

Bagi pereka perkakasan yang berusaha untuk mencapai kebolehpercayaan muktamad, penyahgandingan bekalan kuasa bukan lagi sekadar memilih nilai kapasitans yang betul; ia memerlukan perhatian yang lebih besar terhadap parameter dinamik seperti ESR kapasitor, arus riak dan kestabilan jangka panjang. Kapasitor berbilang lapisan YMIN MPS, melalui teknologi struktur dan bahan yang inovatif, menyediakan jurutera dengan alat yang berkuasa untuk mengatasi cabaran hingar bekalan kuasa. Kami berharap analisis teknikal yang mendalam ini akan memberi anda pandangan. Untuk cabaran aplikasi kapasitor, sila gunakan YMIN.

Masa siaran: 13 Okt-2025